# Pattern Centric Machine Learning Approach to Uncover Process Defects During Wafer Inspection and Review

Yu Zhang, Shirui Yu, Jiaqi Liu, Renyang Meng, Yin Long, Kai Wang, Kun Cai, Xingdi Zhang, Xinghua Song, Jiadong Ren, Shanghai Huali Integrated Circuit Corporation, Shanghai, PRC Abhishek Vikram, Changlian Yan, Guojie Cheng, Hui Wang, Qing Zhang, Wenkui Liao. Anchor Semiconductor Inc (A KLA Company), Santa Clara, USA and Shanghai, PRC

**Invited Presentation**

**International Workshop on Advanced Patterning Solutions**

Dec 12-13, 2021, Foshan, China

- Difficult to manually identify weak patterns based on study of defect Review SEM images

- Tedious to manually check the fix of known weak patterns by guided care area inspection

Incumbent default tool challenges:

- Cannot analyze multiple layers to study full chip design

- Cannot auto analyze SEM images to reliably identify weak patterns

# Solution

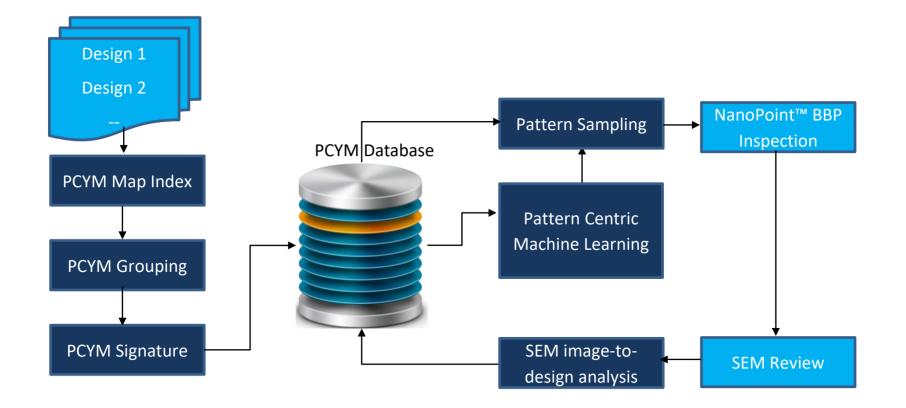

- Review SEM images guide in rule setup for full chip design decomposition and build Pattern Centric Yield Manager Database

- SEM image-to-design analysis perform automated image measurements at target locations to correlate with design and identify weak patterns

- Design and SEM image information enable pattern centric machine learning to rank patterns in PCYM DB and thereby improve sampling

#### **Customer Success:**

- Optimized pattern sampling by automated pattern analytics

- Capability to detect and monitor pattern defects with full chip coverage

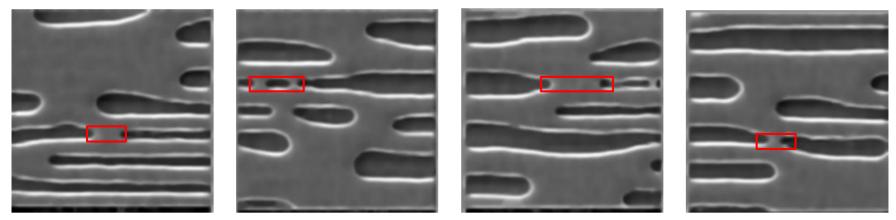

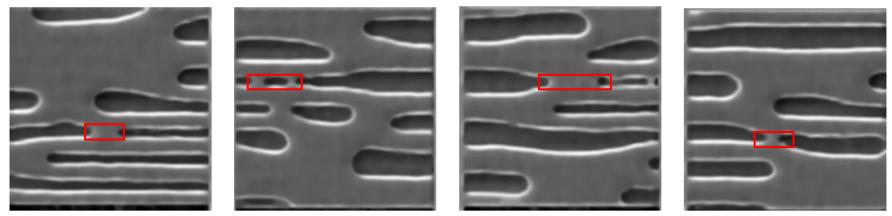

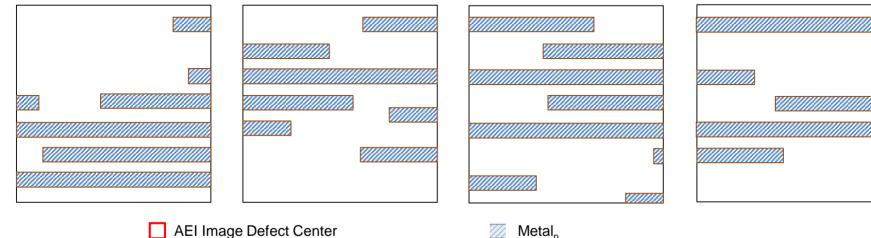

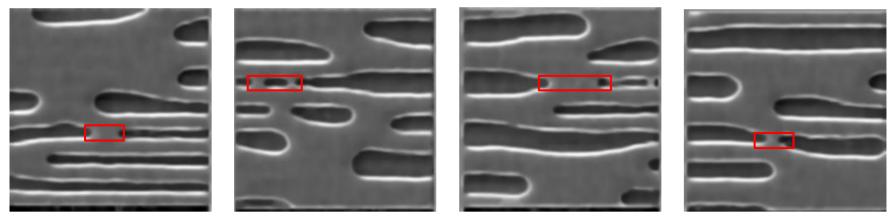

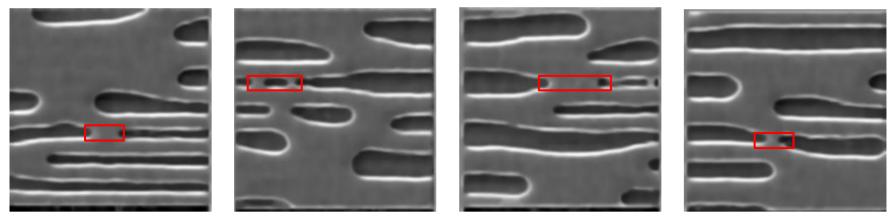

Manual identification of matching with design clip is tedious

- Manual identification of matching with design clip is tedious

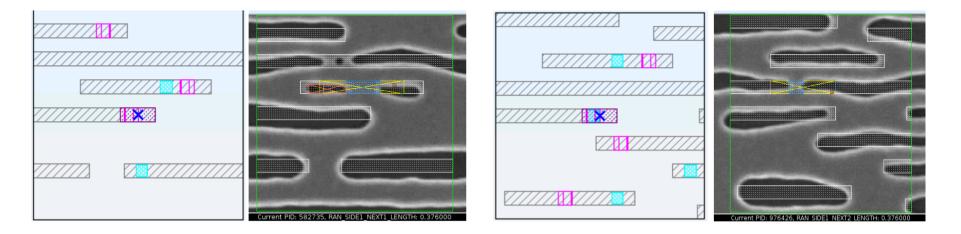

- Visual comparison of SEM image with single layer design does not reveal actionable information

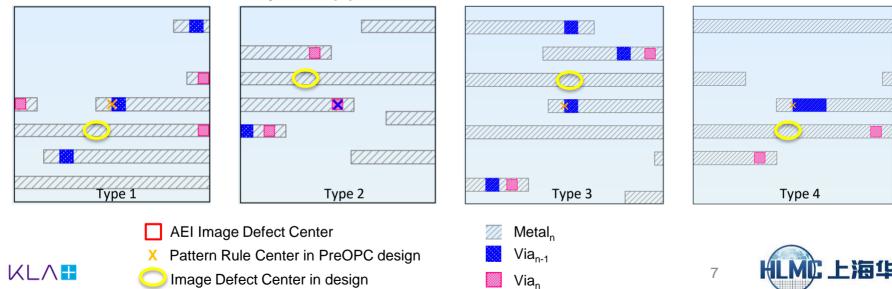

- Layer stack around the defect location does indicate pattern correlation

- Defects occur on long metal polygons that are surrounded by line-ends and is in the vicinity of upper or lower Via

| ι |        | ge Defect Center<br>Rule Center in PreOPC design | <ul> <li>Metal<sub>n</sub></li> <li>Via<sub>n-1</sub></li> <li>Via<sub>n</sub></li> </ul> | 6 HLMC 上海华力 |

|---|--------|--------------------------------------------------|-------------------------------------------------------------------------------------------|-------------|

|   | Type 1 | Туре 2                                           | Туре 3                                                                                    | Type 4      |

|   |        | 777777777777777777777777777777777777777          |                                                                                           |             |

|   |        |                                                  |                                                                                           |             |

|   |        | 7//////////////////////////////////////          |                                                                                           |             |

|   | 2      |                                                  |                                                                                           |             |

|   |        |                                                  |                                                                                           |             |

|   | 22     |                                                  |                                                                                           |             |

|   |        |                                                  |                                                                                           |             |

- Layer stack around the defect location does indicate pattern correlation

- Defects occur on long metal polygons that are surrounded by line-ends and is in the vicinity of upper or lower Via

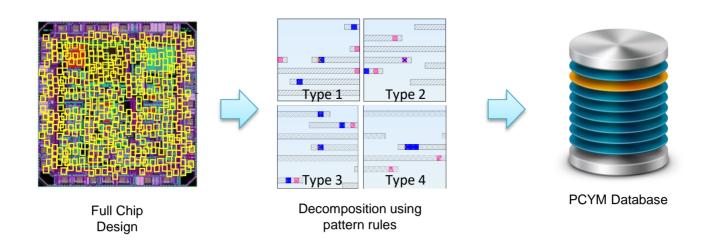

# **PCYM – Full Chip Decomposition**

- Multiple layer design interaction around the defect is captured in pattern rules that is used for full chip design decomposition

- Key design vectors around the defect location are extracted and stored with related pattern information

#### PCML-I: Rank the design vectors

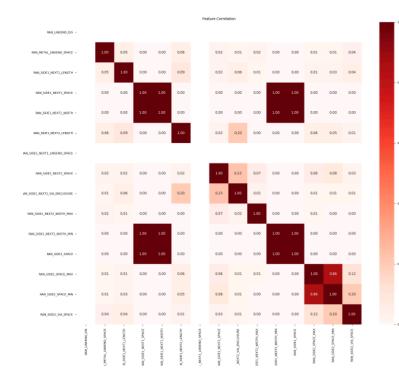

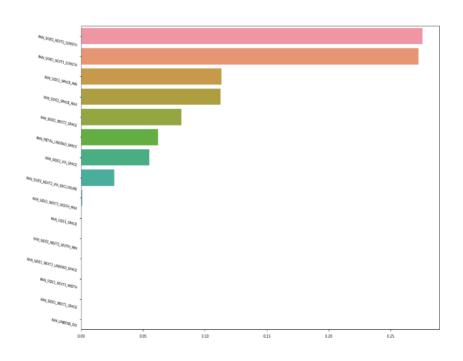

Design vector correlation matrix reveal only 2 vectors redundant

• PCML-I is used to rank the design vectors by importance for each pattern type

| Pattern Type | Count of<br>Signature<br>combination | Count<br>sampled for<br>inspection | Count SEM<br>Reviewed | Sites<br>measured in<br>the SEM<br>images | Sites<br>measured had<br>Pinch defect |

|--------------|--------------------------------------|------------------------------------|-----------------------|-------------------------------------------|---------------------------------------|

| Type 1       | 1026169                              | 1026169 29452                      |                       | 70404                                     | 15137                                 |

| Type 2       | 51259                                | 17203                              |                       | 6155                                      | 615                                   |

| Туре 3       | 46588                                | 16400                              | 4854                  | 4085                                      | 855                                   |

| Туре 4       | 84039                                | 30104                              |                       | 4991                                      | 353                                   |

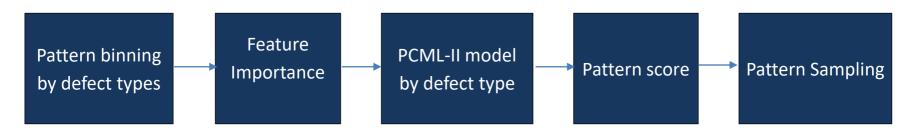

- ML model is built for each pattern type

- Pattern scoring is done for each pattern type

- Final SEM review sampling is limited by the tool budget allocation

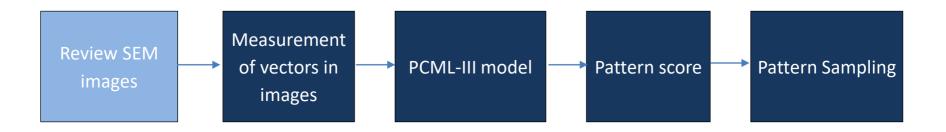

# PCML-III: Image based full chip pattern ranking

- Same vectors are measured on SEM images

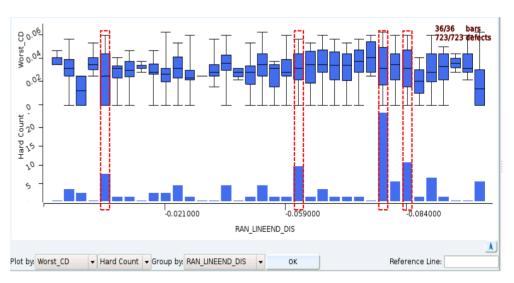

- Variation on wafer is captured by the Box Plot

- Large vector variation correlates with high count of hard defects

- PCML-III model calibration from all SEM image and design data

- PCML-III utilized to rank unseen patterns in PCYM Database

#### Found new weak patterns

- PCML-III prediction of new weak patterns guided care area generation for discovery

- After wafer inspection and standard SEM review found more confirmed weak patterns

✓ PCYM allows translation of multiple layer interaction to build full chip pattern database. It helps to track defects by associated pattern.  $\checkmark$  PCML-I: determined the importance of design vectors by defect type  $\checkmark$  PCML-II: utilized design vectors to build model by defect type and rank patterns with high purity ✓ PCML-III: comprehensive SEM image measurement for the same design vectors help to correlate with wafer defect occurrence and ranked rest of the patterns in PCYM DB

✓ Identified new weak patterns

[1] Khurram Zafar, Chenmin Hu, Ye Chen, Yue Ma, Chingyun Hsiang, Justin Chen, Raymond Xu, Abhishek Vikram, Ping Zhang, "Pattern weakness and strength detection and tracking during a semiconductor device fabrication process", US Patents #9,846,934 (2017), #10,062,160 (2018).

[2] Khurram Zafar, Chenmin Hu, Ye Chen, Yue Ma, Chingyun Hsiang, Justin Chen, Raymond Xu, Abhishek Vikram, Ping Zhang, "Pattern weakness and strength detection and tracking during a semiconductor device fabrication process", Taiwan Patents #I608427(2017), #I634485 (2018).

[3] Chenmin Hu, Khurram Zafar, Chen Ye, Ma Yue, Lv Rong, Justin Chen, Abhishek Vikram, Yuan Xu, Ping Zhang, "Pattern Centric Process Control", US Patent 10,546,085 (2020).

[4] Chenmin Hu, Khurram Zafar, Abhishek Vikram, Geoffrey Ying, "Pattern-Centric Computational System for Logic and Memory Manufacturing and Process Technology Development", Journal of Microelectronics Manufacturing, Vol 3 (4): 20030410, 2020.

[5] Li-Fu Chang, Chang-Il Choi, Guojie Cheng, Abhishek Vikram, Gary Zhang, and Bo Su, "Detection of OPC conflict edges through MEEF analysis", Proc. SPIE 7641, Design for Manufacturability through Design-Process Integration IV, 764111, 2010.

[6] Eric Guo, Shirley Zhao, Skin Zhang, Sandy Qian, Guojie Cheng, Abhishek Vikram, Ling Li, Ye Chen, Chingyun Hsiang, Gary Zhang, and Bo Su, "Simulation based mask defect repair verification and disposition", Proc. SPIE 7488, Photomask Technology 2009, 74880G, 2009.

[7] Eric Guo, Irene Shi, Blade Gao, Nancy Fan, Guojie Cheng, Li Ling, Ke Zhou, Gary Zhang, Ye Chen, Chingyun Hsiang, and Bo Su, "Simulation based mask defect printability verification and disposition, part II", Proc. SPIE 8166, Photomask Technology 2011, 81662D, 2011.

[8] Gyun Yoo, Jungchan Kim, Taehyeong Lee, Areum Jung, Hyunjo Yang, Donggyu Yim, Sungki Park, Kotaro Maruyama, Masahiro Yamamoto, Abhishek Vikram, Sangho Park, "OPC verification and hotspot management for yield enhancement through layout analysis", Metrology, Inspection, and Process Control for Microlithography XXV, Proc. of SPIE Vol. 7971, 79710H, 2011.

[9] Taehyeong Lee, Hyunjo Yang, Jungchan Kim, Areum Jung, Gyun Yoo, Donggyu Yim, Sungki Park, Akio Ishikawa, Masahiro Yamamoto, Abhishek Vikram, "Hot spot management through design-based metrology: measurement and filtering", Proc. SPIE. Vol. 7520, 75201U, 2009.

#### References

[10] Sicong Wang, Jian Mi, Abhishek Vikram, Gao Xu, Guojie Cheng, Liming Zhang, Pan Liu, "Novel pattern-centric solution for high performance 3D NAND VIA dishing metrology", Design-Process-Technology Co-optimization for Manufacturability XIII, SPIE Vol. 10962, 1096217, 2019.

[11] Jing Zhang, Qingxiu Xu, Xin Zhang, Xing Zhao, Jay Ning, Guojie Cheng, Shijie Chen, Gary Zhang, Abhishek Vikram, Bo Su, "Yield impacting systematic defects search and management", Design for Manufacturability through Design-Process Integration VI, Proc. of SPIE Vol. 8327, 832716, 2012.

[12] Qian Xie, Panneerselvam Venkatachalam, Julie Lee, Zhijin Chen, Khurram Zafar, "Design guided data analysis for summarizing systematic pattern defects and process window", Proc. SPIE. 9778, Metrology, Inspection, and Process Control for Microlithography XXX Proceedings Article, 2016.

[13] Qian Xie, Panneerselvam Venkatachalam, Julie Lee, Zhijin Chen, Khurram Zafar, "Precise design-based defect characterization and root cause analysis", Proc. SPIE. 10145, Metrology, Inspection, and Process Control for Microlithography XXXI Proceedings Article, 2017.

[14] Ming Tian, Yu Zhang, Tiapeng Guan, Jianghua Leng, Baojun Zhao, Lei Yan, Wei Hua, Abhishek Vikram, Guojie Chen, Hui Wang, Gary Zhang, Wenkui Liao, "Critical Defect Detection, Monitoring and Fix through Process Integration Engineering by Using D2DB Pattern Monitor Solution", Design-Process-Technology Co-optimization for Manufacturability XIII, SPIE Vol. 10962, 109620L, 2019.

[15] Lijun Chen, Jun Zhu, Xuedong Fan, Haichang Zheng, Xiaolong Wang, Yancong Ge, Yu Zhang, Abhishek Vikram, Guojie Cheng, Hui Wang, Qing Zhang, Wenkui Liao, "An Advanced and Efficient Methodology for Process Setup and Monitoring by Using Process Stability Diagnosis in Computational Lithography", Design-Process-Technology Co-optimization for Manufacturability XIV, Proc. SPIE. 11328, 2020.

[16] Abhishek Vikram, Kuan Lin, Janay Camp, Sumanth Kini, Frank Jin, Vinod Venkatesan, "Inspection of high-aspect ratio layers at sub 20nm node", Metrology, Inspection, and Process Control for Microlithography XXVII, Proc. of SPIE Vol. 8681, 86811Q, 2013.

[17] Yu Zhang, Shirui Yu, Jiaqi Liu, Renyang Meng, Yin Long, Kai Wang, Kun Cai, Xingdi Zhang, Xinghua Song, Jiadong Ren, Abhishek Vikram, Changlian Yan, Guojie Cheng, Hui Wang, Qing Zhang, Wenkui Liao, "Pattern Centric Yield Management Approach with Machine Learning to Detect and Track Defects with Full Chip Coverage", Proc. SPIE. 11614, Design-Process-Technology Co-optimization XV, 2021.